集成電路產(chǎn)業(yè)作為電子信息產(chǎn)業(yè)的核心,是關系國民經(jīng)濟和社會發(fā)展的,具有基礎性、先導性和戰(zhàn)略性的產(chǎn)業(yè)����,是衡量國家科技水平和創(chuàng)新能力的重要標志����,受到眾多國家的高度重視,也是發(fā)達國家實施技術(shù)封鎖的重點���。集成電路微細化制程技術(shù)日新月異���,結(jié)構(gòu)尺寸從微米推向深亞微米,進而邁入納米時代����。目前國際主流技術(shù)已從14nm技術(shù)向10nm、7nm����、5nm甚至3nm逐步遞進,代表公司有臺積電���、三星����、英特爾等。中國目前生產(chǎn)線較為成熟的技術(shù)是45nm和28nm��,領先技術(shù)達到14nm�。隨著集成電路線寬世代的發(fā)展����,對用于沉積芯片互連線的靶材也提出了更高的要求。

先進制程集成電路制備工藝中廣泛采用Ta/TaN擴散阻擋層與Cu互連線搭配使用����,隨著芯片的集成度與日俱增,特別是技術(shù)節(jié)點發(fā)展至7nm及以下���,Ta/TaN阻擋層的厚度必須足夠薄以實現(xiàn)高集成度芯片的功能性��,這對鉭靶材的各項性能��,尤其是晶向均勻性提出了極高的要求�����。鉭的晶向會明顯影響濺射速率�����,最終影響沉積薄膜厚度的均勻性[1]���,研究發(fā)現(xiàn)�����,鉭各織構(gòu)面濺射速率關系為{110}>{100}>{111}���。目前行業(yè)中主流使用的是軋制鉭靶材,實際濺射使用過程中會遇到大量的因晶向不匹配產(chǎn)生的問題���。粉末冶金技術(shù)廣泛應用于陶瓷靶材的制備����,用于制備鉭靶材的僅國外少數(shù)幾家公司����,其在某些方面的優(yōu)越性可能會成為14nm及以下技術(shù)節(jié)點集成電路用鉭靶材的主要制備技術(shù)。文章研究對比了軋制鉭靶材與粉末冶金鉭靶材的晶向和晶粒�����,為先進制程用鉭靶材的開發(fā)提供一些參考����。

1����、實驗材料和方法

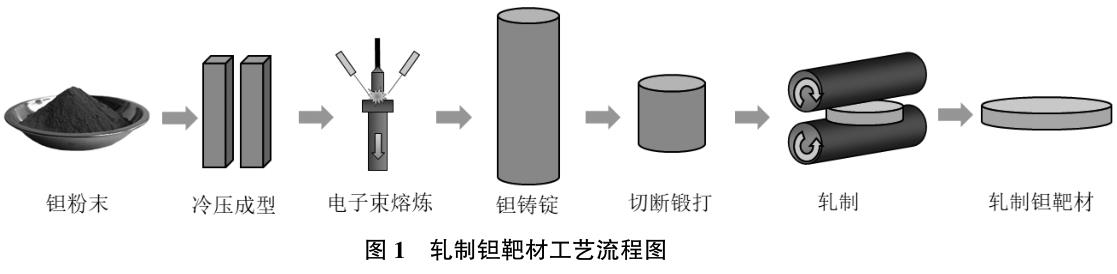

軋制鉭靶材實驗原料采用純度為99.95%以上的高純鉭粉末�����。高純鉭粉末經(jīng)300MPa冷等靜壓后形成具有一定致密度的坯料���,坯料通過電子束熔煉制成鑄錠,將鑄錠頭尾兩端缺陷部分切除后進行鍛打和軋制�����,得到最終樣品尺寸φ500mm×8mm�����。軋制鉭靶材的工藝流程如圖1所示�。

粉末冶金鉭靶材實驗原料采用與軋制鉭靶材相同的純度為99.95%以上的高純鉭粉末。高純鉭粉末經(jīng)300MPa冷等靜壓形成基本的圓形坯料����,將坯料用不銹鋼包套密封后置于熱等靜壓設備中燒結(jié)���,環(huán)境壓力200MPa,溫度1300℃��,最終得到尺寸同樣為φ500mm×8mm��,致密度大于99%的樣品����。粉末冶金鉭靶材的工藝流程如圖2所示。

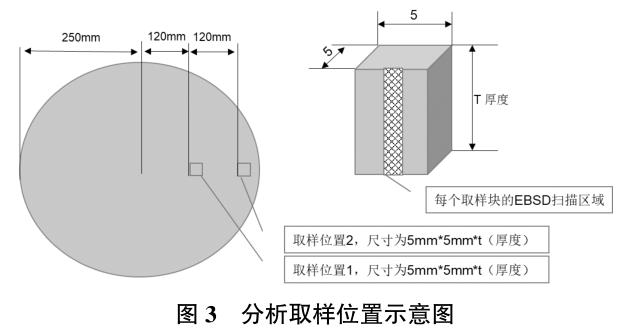

每個靶材按照圖3所示位置各取2個分析樣��,分析樣品的尺寸為5mm×5mm×t(厚度約8mm)�����。將分析樣品的檢測面研磨至沒有明顯劃痕�����,用H2SO4∶HNO3∶HF=3∶2∶2(體積比)的腐蝕液腐蝕檢測面約30s���,腐蝕完成后用水將表面沖洗干凈��。采用日立SU3500掃描電子顯微鏡(SEM)搭載牛津NordlysMax3電子背散射衍射儀(EBSD)測試靶材斷面的晶向��。其基本原理是利用滿足布拉格衍射條件(2dsinθ=nλ)的背散射電子得到一系列菊池花樣���,根據(jù)菊池花樣的特點得出晶面間距和晶面之間的夾角����,然后從數(shù)據(jù)庫中查找相關的晶體結(jié)構(gòu)和晶胞參數(shù)�����,最終以不同方向占比以及極圖強度來表征織構(gòu)[2-3]���。另外采用OlympusPME3型倒置式金相顯微鏡觀察微觀晶粒,依據(jù)標準GB/T6394—2002�����,使用直線截點法計算平均晶粒度�。

2、實驗結(jié)果和分析

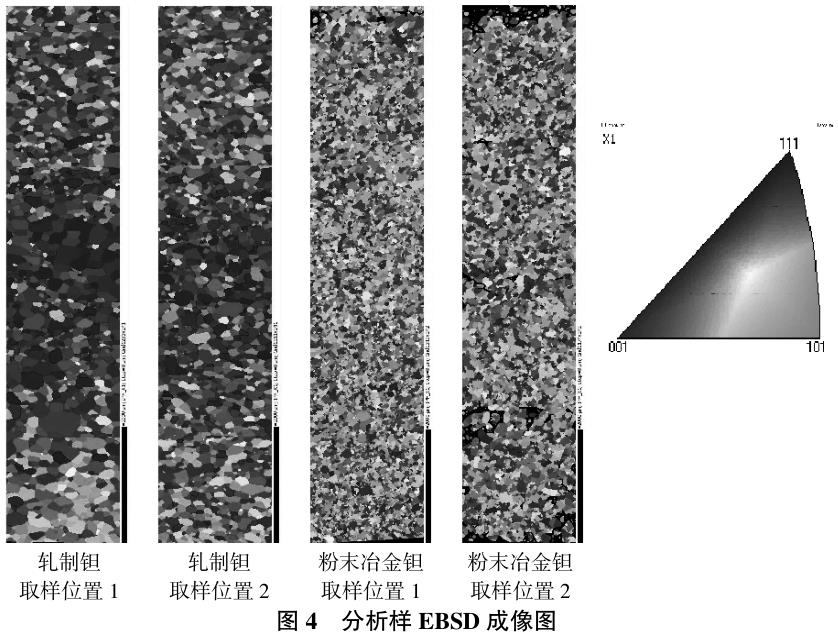

樣品EBSD分析結(jié)果如圖4所示�����,不同顏色代表不同晶面取向����,對于具有體心立方結(jié)構(gòu)的鉭材料主要比較{100}��、{110}�、{111}三種晶面的占比����。從分析結(jié)果圖中可以看到,軋制鉭的整個斷面晶向分布不均勻����,取樣位置1和取樣位置2都存在二分之一厚度附近{111}偏多的現(xiàn)象。而粉末冶金鉭靶材的晶向則相對比較均勻����,取樣位置1和取樣位置2各晶面占比沒有明顯差異。

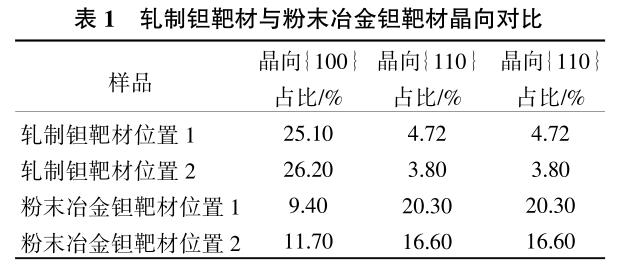

統(tǒng)計4個分析樣品的晶向占比�,結(jié)果如表1所示。

從表1的數(shù)據(jù)可以發(fā)現(xiàn)�,軋制鉭三種晶向占比相差較大,軋制鉭靶材位置1的{111}占比最大為36.7%����,{110}占比最小僅4.72%,兩者相差31.98%�;軋制鉭靶材位置2的{100}和{111}占比均為26.20%�,遠大于{110}僅3.80%的占比��,差值22.40%�。而粉末冶金鉭三種晶向占比差距較小,粉末冶金鉭靶材位置1的{110}占比最大為20.3%��,{100}占比最小為9.40%��,相差不足11%��;粉末冶金鉭靶材位置2的{110}占比最大為16.6%����,{100}占比最小為11.70%�,相差僅4.90%。

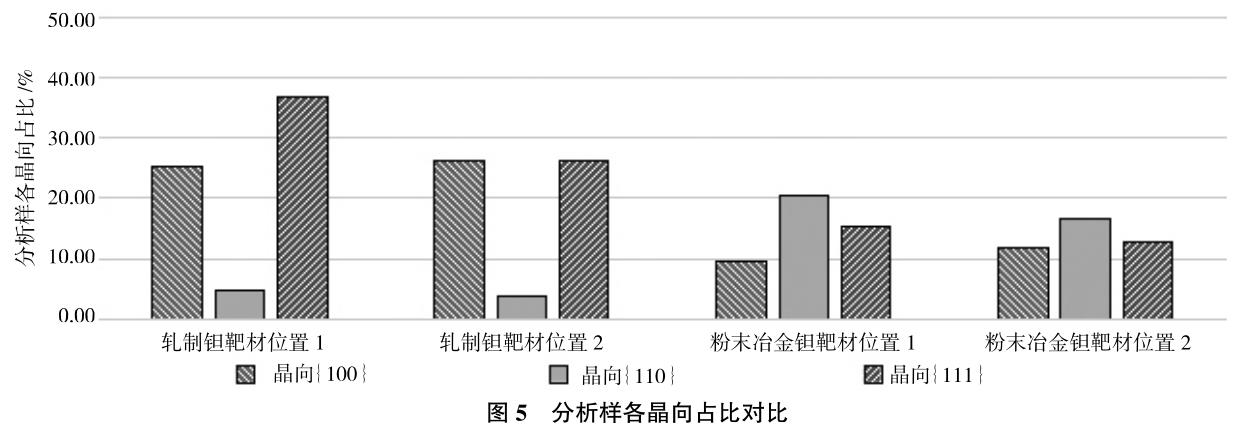

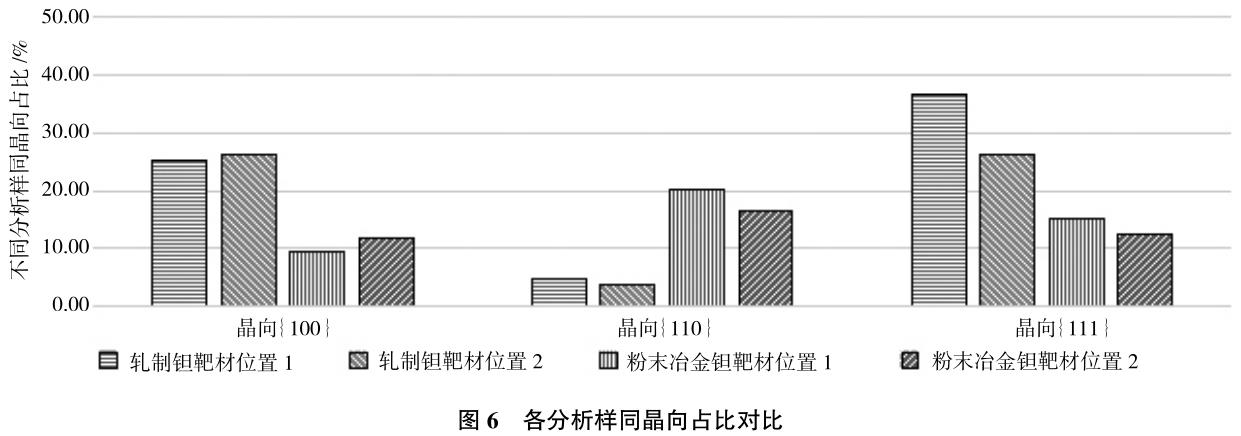

每個分析樣各晶向占比如圖5所示����,從圖5可以明顯看出粉末冶金鉭靶材的晶向均勻性要遠好于軋制鉭靶材。比較不同分析樣同種晶向的占比�����,如圖6所示�����,發(fā)現(xiàn)軋制鉭靶材{100}和{111}明顯占優(yōu),都遠高于粉末冶金鉭靶材���;而粉末冶金鉭靶材各晶向占比均勻����,2個樣都只有{110}占比會高于該面不占優(yōu)的軋制鉭靶材��。

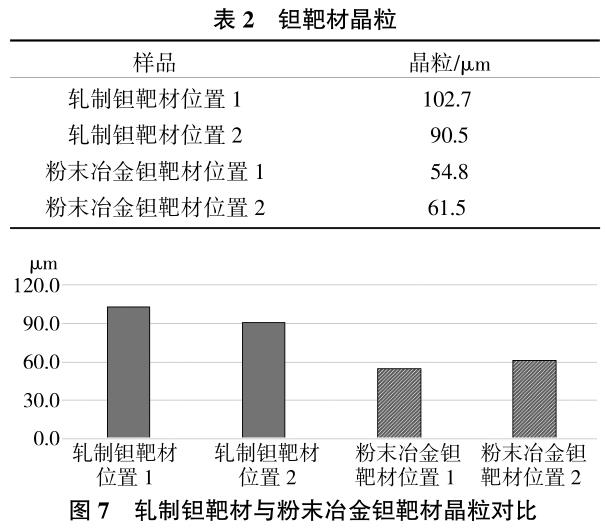

統(tǒng)計分析4個分析樣品的平均晶粒����,結(jié)果如表2和圖7所示。從圖表中可以發(fā)現(xiàn)���,粉末冶金鉭靶材的晶粒要小于軋制鉭靶材����,且粉末冶金鉭靶材兩個分析樣的晶粒差值不到7μm���,小于軋制鉭靶材兩個分析樣的差值��,這也一定程度上說明粉末冶金鉭靶材晶粒均勻性可能會稍優(yōu)于軋制鉭靶材���。

3�����、結(jié)論

(1)軋制鉭靶材不同取樣位置的晶向差異較大�����,即便是同一個取樣位置��,整個斷面上�����、中����、下的晶向也存在不均勻現(xiàn)象����。而粉末冶金鉭靶材不同取樣位置的晶向比較均勻�����,同一個取樣位置,整個斷面的上��、中���、下也相對均勻一致��。粉末冶金鉭靶材晶向的均勻性要優(yōu)于軋制鉭靶材���。

(2)軋制鉭靶材的晶粒在90~103μm,粉末冶金靶材的晶粒在54~62μm�����,軋制鉭靶材的晶粒大于粉末冶金鉭靶材�����。

(3)從晶粒晶向的均勻性來說���,粉末冶金鉭靶材要優(yōu)于軋制鉭靶材�����,粉末冶金工藝可能會成為14nm及以下技術(shù)節(jié)點集成電路用鉭靶材的主要制備技術(shù)�����。

參考文獻

[1]Michaluk A C .Correlating discrete orientation and grain size to the sputter deposition properties of tantalum[J].Journal of Elec-tronic Materials�,2002,31(1):2-9.

[2]毛衛(wèi)民�,楊平,陳冷.材料織構(gòu)分析原理與檢測技術(shù)[M].北京:冶金工業(yè)出版社��,2008.

[3]楊平.電子背散射衍射技術(shù)及其應用[M].北京:冶金工業(yè)出版社���,2007.

相關鏈接