引言

鎢材料具有抗電子遷移能力強��、電阻率低���、高溫穩(wěn)定性好、導熱及導電性能優(yōu)良等特性�����,是集成電路芯片制備過程中一類重要的基礎材料����。 鎢材料主要以薄膜的形式應用在半導體器件中����, 被用作高傳導性的互連金屬����、金屬層間的通孔、垂直接觸的接觸孔中的填充物(W plug���,鎢插塞)以及硅和鋁間的隔離層[1-2]���。 鎢薄膜的制備技術主要包括物理氣相沉積(PVD,主要指濺射沉積)和化學氣相沉積(CVD)���。 由于 CVD 制備薄膜的階梯覆蓋能力強�����,可以很好地填充通孔�����, 因此主要應用在接觸孔鎢插塞的制備工藝中��。 與 CVD 工藝相比����,PVD 工藝沉積的鎢薄膜具有純度高、致密性好�、膜層厚度更均勻、電阻率更低的優(yōu)勢����,主要應用于制備集成電路的擴散阻擋層����、黏結層和存儲器的柵極組件。 PVD 技術具有沉積速率高��、污染少��、操作過程簡便等特點����,越來越引起人們的重視。

靶材是 PVD 濺射沉積薄膜的原材料��。世界半導體貿易統(tǒng)計協(xié)會(World Semiconductor Trade Statistics���,WSTS)的統(tǒng)計數(shù)據(jù)顯示[3]�����,2016 年全球濺射靶材市場容量達 113.6 億美元�����,預計 2020 年全球濺射靶材市場規(guī)模將超過 163 億美元���。 全球靶材應用領域中��,雖然半導體行業(yè)用濺射靶材的消耗量只占 10 %�,但是由于半導體行業(yè)對于靶材性能要求的高標準��,使得半導體領域用靶材的制備技術難以突破[4]�����。

隨著半導體技術的不斷發(fā)展����, 集成電路中的晶體管和線寬的尺寸越來越小。 芯片制程工藝已經(jīng)從130nm提升至 7nm����,更高端的芯片制程工藝也時有報道����。 為了滿足現(xiàn)代芯片高精度��、小尺寸的需求�����,對電極和連接器件的布線金屬薄膜的性能要求越來越高�����,這就對濺射靶材的性能提出了更高的要求�����。本文主要對集成電路用鎢濺射靶材的性能要求���、 制備技術進行綜述,并對鎢靶材的發(fā)展做出預測�。

1、集成電路用鎢靶材的性能要求

集成電路芯片制造領域用鎢濺射靶材對材料的純度����、致密性���、晶粒尺寸及均勻性、織構等方面均具有嚴格的要求�。

1.1純度

高純度甚至超高純度靶材是高端集成電路半導體芯片的必備材料。 鎢靶材的純度決定了鎢薄膜的純度���,一般來講����,其純度需≥99.999 %(5N)[5]����。 鎢靶材中的雜質會在濺射沉積過程中進入鎢薄膜, 薄純度的降低將導致其電阻率的增加���, 同時會造成薄膜均勻性不佳等問題�, 最終對器件的良品率造成不利的影響�。 Glebovsky[6-7]研究表明,鎢靶材中堿金屬(Na�����,K,Li)含量過高���,會直接影響鎢薄膜的電遷移性能�。而且�����,堿金屬離子擴散進入二氧化硅絕緣層會成為可動離子���,將增加柵極絕緣材料泄露的風險����,降低器件的可靠性��, 通常靶材的堿金屬含量應控制在0.1×10-6 以內[8]�。 此外����,氧含量對鎢薄膜性能具有至關重要的影響, 氧含量過高容易導致薄膜沉積過程中形成微粒和液滴�,造成薄膜缺陷和電路短路,從而引起器件的失效[9]���;同時�,鎢薄膜中的氧含量過高也會增加薄膜的電阻率,從而影響信號的傳輸速率[10]�。

集成電路用鎢濺射靶材的氧含量應控制在≤100×10-6,針對部分更高端的應用�, 靶材中的氧含量應≤20×10-6[11]。 因此�����,半導體行業(yè)的不斷發(fā)展對靶材提出了越來越高的要求����, 需要我們持續(xù)降低靶材中雜質元素的含量,提升靶材的純度�。

1.2相對密度

集成電路用濺射靶材的致密性越高越好,一般來講���,半導體行業(yè)要求鎢靶材的真實密度≥19.15g/cm3�,相對密度≥99.5 %[8]���。 但是�����,通過傳統(tǒng)粉末冶金工藝制備的鎢靶材呈現(xiàn)多孔結構����,難以得到相對密度高的板坯。靶材中的孔洞在濺射過程中會產(chǎn)生不均勻沖蝕現(xiàn)象�,這是濺射過程中發(fā)生微粒現(xiàn)象的主要原因[12]�。

薄膜中的微粒越多,器件的良品率越低��。 Chi-Fung Lo等[13]研究表明����,具有較低相對密度的鎢靶材,不僅在濺射時容易形成微粒�, 而且會引起薄膜電阻率升高等問題,進而影響鎢薄膜的性能��,具體來說�����,鎢靶材致密性低會導致濺射的薄膜呈薄片狀����, 從而增大了薄膜應力,造成晶界取向差�,進而增加了薄膜的電阻率。 此外��,鎢靶材的相對密度越高�����,薄膜的沉積速率越快����,從而提升靶材濺射效率。 因此�,獲得致密性優(yōu)良的鎢靶材是濺射沉積得到具有低電阻率鎢薄膜的重要前提。

1.3晶粒

細晶靶材的濺射沉積速率及成膜均勻性均優(yōu)于粗晶靶材��,因此鍍膜設備商通常偏愛細晶靶材���。對高純鎢材料(≥99.999%)而言���,細晶鎢靶材的制備難度極大, 這是因為高純金屬內沒有可以阻止晶粒長大的第二相粒子�, 同時高純金屬在相變時形核核心數(shù)量少,形核率低�,導致晶粒難以細化[14]����。 因此�����,集成電路用高純鎢靶材的晶粒度要求通常需≤100 μm���。

除晶粒尺寸外��,提升靶材中晶粒均勻性同樣重要�����,其直接影響濺射效率和沉積薄膜的均勻性���, 而晶粒尺寸的均勻性需從徑向和軸向兩個維度來進行評價。

因此��,減小靶材晶粒尺寸����、同時提升晶粒尺寸的均勻性,是靶材制備領域一個重要的研究方向����。

1.4織構

鎢靶材的織構(多晶體的晶粒取向分布規(guī)律)對濺射薄膜的影響往往被人們所忽視, 它對濺射沉積而成的薄膜厚度均勻性具有顯著的影響�。Takafumi[15]研究表明,用作集成電路柵極材料的鎢薄膜���,其厚度的差異將影響柵極電阻率的穩(wěn)定性�, 從而影響晶體管的性能���,最終降低集成電路的良品率�。 目前�,濺射得到鎢薄膜的厚度變化僅能控制在3%左右, 為了進一步提升芯片的集成度�����、運行速度和可靠性�,對鎢薄膜的厚度均勻性提出了更高的要求(≤1 %)[16]。鎢靶材是多晶結構��, 其濺射沉積得到薄膜厚度的均勻性與靶材單個晶體的取向分布有很大的關系�。因此,應保證鎢靶材厚度方向上的織構在整個靶材濺射生命周期內的均勻性��。此外,為了確保鎢靶材織構批次間的穩(wěn)定性�����,產(chǎn)品一旦被客戶驗證通過��,其制備工藝隨之固定�,并且不可輕易更改。

2�����、集成電路用鎢靶材的制備技術

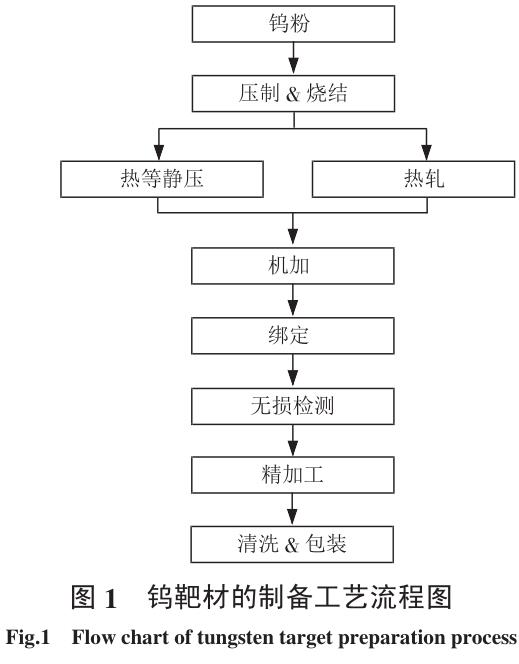

由于鎢材料熔點高和脆性大���, 鎢靶材的整個制備工藝流程主要沿用傳統(tǒng)的粉末冶金工藝����。 如圖 1所示�����,從鎢粉到靶材����,需要進行兩次致密化處理�����。 第一次致密化不論是通過冷等靜壓 (CIP) 還是熱壓(HP)工藝,其制備得到坯體的致密度均偏低��,所以通常需要進行二次致密化來提升其相對密度�����。目前�,最常見的二次致密化工藝是熱等靜壓(HIP)和熱軋(Hot Rolling)[17-20]。 得到高致密度的鎢板后�,需進行切割及表面處理, 然后再和導電及導熱性能優(yōu)良且具有一定強度的背板綁定[21]�����,進而通過超聲無損探傷(C-SCAN)進行焊合率的檢驗(≥95 %)����,最后通過精密加工,無塵清洗��、包裝后達到電子級要求�����,成為合格的靶材產(chǎn)品。

為了制備致密度高�����、 晶粒均勻且氧含量低的鎢板�,國內外研究者[22-30]采用不同的熱機械處理工藝進行鎢板材的制備, 其中主要為以熱等靜壓和熱軋為主流的二次致密化工藝�����, 下面將逐一介紹這兩種工藝及其組合����。

2.1熱等靜壓(HIP)工藝

熱等靜壓工藝是指在鎢靶材致密化工序中引入熱等靜壓技術。 熱等靜壓技術是一種不同于傳統(tǒng)無壓或者熱壓致密化的工藝技術���,產(chǎn)品在致密化時��,被施以各向同等的壓力�,在高溫高壓的共同作用下����,產(chǎn)品得到致密化�,從而得到致密性高�����、組織結構均勻的靶材產(chǎn)品���。

美國 Praxair 公司的 Lo 等[22]采用 HIP 工藝進行鎢板的制備。 選用粒徑<10 μm 的鎢粉�����,工藝溫度1 400 ℃�����,保溫時間 7 h�����,壓力 276 MPa�。 選用包套材料的熔點需高于熱等靜壓的工藝溫度, 常用的包套材料包括鈦��、 鐵等。 作者采用該工藝得到了氧含量≤300×10-6 且相對密度達 97 %的鎢板����, 此外,通過細化鎢粉的粒徑�,可進一步提升鎢板的相對密度。但是����,如果板坯的直徑超過厚度 3 倍以上,則需要在HIP 工藝前加入 CIP 工藝����,以確保鎢板的致密度。

為了進一步提升鎢濺射靶材的致密性�����, 研究者在熱等靜壓之前���,先對生坯進行一次致密化����,一次致密化工藝主要包括冷等靜壓�、真空常壓燒結�、熱壓燒結等�,進而再采用熱等靜壓技術對坯體進行二次致密化,這種方法有助于得到相對密度≥99 %的鎢靶材�。

日本 Nippon Tungsten 公司的 Shibuya 等[23]通過組合 CIP 和 HIP 兩種工藝過程, 進行鎢靶材的制備����。 首先采用 CIP 工藝壓制鎢粉(粒徑 0.5~4 μm),壓力≥350 MPa�,得到鎢生坯;再通過除氣和燒結工藝(溫度≥1 600 ℃�����,保溫時間≥5 h)得到鎢燒結坯(密度 18.8 g/cm3)���;最后采用 HIP 工藝進行二次致密化,溫度≥1 900 ℃�����,壓力≥150 MPa��。 最終得到了密度為 19.28 g/cm3 的板坯���。 利用這套制備工藝得到的板坯孔隙率低���,微觀組織均勻��,且晶粒具有各向同性的特征��,平均晶粒尺寸僅為 15 μm�。

日本 Nikko Materials 公司的 Suzuki[24]結合 HP和HIP 工藝�����,進行高致密鎢靶材的制備研究��。 首先采用HP 工 藝 制 備 燒 結 坯(溫 度1600 ℃ ��, 壓 力≥200 kg/cm2)����,坯體的相對密度可達 93 %;進而利用 HIP 工藝進行板坯的二次致密化(溫度1700 ℃��,壓力≥1000 kg/cm2)�, 板坯的相對密度達到 99 %以上,平均晶粒尺寸≤100 μm�����,氧含量≤20×10-6。

2.2熱軋(Hot Rolling)工藝

軋制屬于金屬變形加工工藝��, 而熱軋是指在材料的再結晶溫度以上進行的軋制���。一般來講����,通過常規(guī)粉末燒結技術難以獲得高致密的鎢材料����, 熱軋技術是一種有效地、 可以進一步提升鎢燒結體致密性的方法��;此外�,通過熱軋��,可以有效地調控基體的顯微結構���。

美國 Tosoh 公司的 Ivanov 等[25�,30]結合 HP 和熱軋工藝�, 進行高致密鎢靶材的制備研究�����。 首先采用HP 工藝制備得到相對密度為95%的燒結坯�, 再利用熱軋工藝進一步提升鎢板的致密度����。 軋制溫度為1 400~1 700 ℃,累計變形量>40 %���,最終得到相對密度≥97.5 %的鎢板����,板坯的平均晶粒尺寸≤100 μm�,氧含量≤100×10-6。

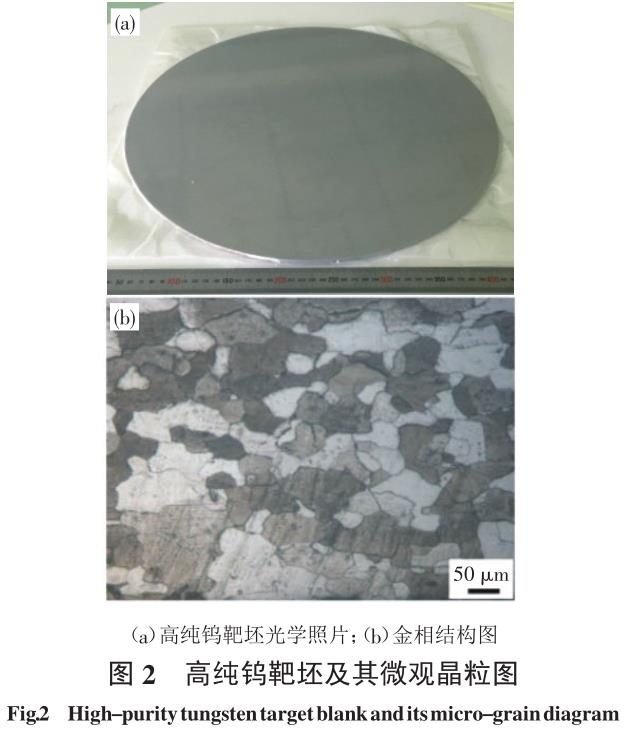

廈門虹鷺鎢鉬工業(yè)有限公司采用粉末冶金和壓力加工的工藝路線進行高純鎢靶材的制備�。 虹鷺具備生產(chǎn)純度≥99.999 9 %(6N) 超高純鎢粉的能力,選用超高純鎢粉為原料進行鎢靶坯的制備���, 得到靶坯的純度可達 99.999 5 %(5N5)以上�����,且相對密度≥99.5 %�����,氧含量<10×10-6��,晶粒尺寸≤50 μm(見圖 2)�����,鎢靶材綜合性能達到國外同類產(chǎn)品的水平�����。

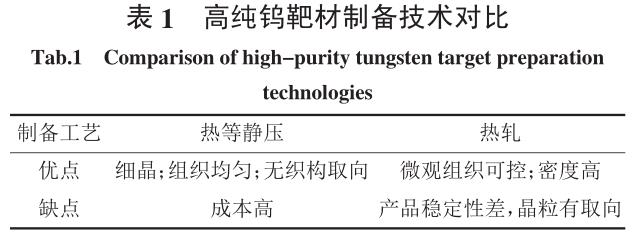

高純鎢靶材制備技術的特點總結如表 1 所示����。

采用 HIP 工藝制備鎢靶材,可以有效地控制晶粒的大小�,有助于得到晶粒細小的鎢靶材;該工藝加熱過程均勻���,有助于獲得組織結構均勻的鎢靶材,并且晶粒不具有取向性�����, 因而更容易通過濺射得到一致性好的鎢薄膜;此外 HIP 工藝針對脆性大的鎢材料有更好的壓縮成型的作用�����;但是����,HIP 工藝需要的熱等靜壓爐和高純包套材料(適用于鎢材料)的價格異常昂貴,這成為制約 HIP 工藝在靶材制備方面推廣的主要原因��。 相對于 HIP 工藝�����,熱軋工藝制備得到的鎢靶材具有晶粒大小可控的特性���;然而�����,該工藝步驟多�����,參數(shù)波動因素大����,人為操作引起的誤差較大,產(chǎn)品質量的一致性不高�����, 并且軋制容易導致織構的取向性�;但從另一方面看,可以通過控制軋制工藝來調整靶材的織構取向�����,獲取具有最優(yōu)織構取向的靶材����,從而達到提升鎢靶材濺射性能的目的。

3�、未來的發(fā)展趨勢預測

根據(jù)超大規(guī)模集成電路(VLSI)技術發(fā)展的趨勢,芯片制造的要求越來越嚴格�,集成電路的集成度越來越高,特征尺寸越來越小�����。 PVD 濺射而成鎢薄膜的優(yōu)點(純度高,致密性好�,膜層均勻)正好可以匹配集成電路上柵極和布線材料小而精的發(fā)展需求���。

但是�, 鎢靶材濺射制備的薄膜的電阻率達到了鎢材料電阻率的 2 倍���, 進一步降低鎢薄膜的電阻率是芯片制造商提出的重要需求�, 也必將會成為一個重要的研究方向���。

日本 JX Nippon Mining & Metals 公司的 Ohashi[31]和 Kaminaga[32]對如何降低鎢薄膜的電阻率進行了深入的研究���, 主要采取的方法是對鎢靶材基體中的微量元素進行分析,研究發(fā)現(xiàn)��,通過控制碳元素和鉬元素的含量�,可以有效地降低鎢薄膜的電阻率。 此外�,為了滿足濺射薄膜的均勻性和最大程度減少微粒飛濺, 鎢靶材的微觀組織均勻性是另一個重要的研究方向�����。 鎢晶粒在制備過程中異常長大容易降低板材及其晶界的強度,破壞微觀組織均勻性�����,因此 Suzuki[33-34]和 Ohashi[35]通過調控鎢基體中的磷元素和鐵元素�,可以有效地抑制鎢晶粒的異常生長, 從而成功地降低了鎢靶材的晶粒尺寸��, 最終提升了靶材的濺射效率和鎢薄膜的均勻性�����。

基于以上分析���,筆者預計未來鎢濺射靶材的發(fā)展趨勢及目標如下:(1)提升靶材純度�����,≥6N���;(2)降低靶材氧含量,≤5×10-6���;(3)減小靶材晶粒尺寸��,同時提高其織構均勻性���;(4)降低沉積鎢薄膜的電阻率��。目前具備規(guī)模化生產(chǎn)集成電路用鎢靶材的企業(yè)數(shù)量相對較少�,主要分布在美國和日本,產(chǎn)業(yè)集中度高���。 這些跨國集團產(chǎn)業(yè)鏈完整����,具有包括金屬提純�、靶材制造、 濺射鍍膜和終端應用等各個環(huán)節(jié)的規(guī)?�;a(chǎn)能力�����, 它們在掌握先進技術以后實施技術壟斷和封鎖���,主導著技術革新和產(chǎn)業(yè)發(fā)展�����。高純鎢靶材比較成熟的制備工藝主要包括熱等靜壓及熱軋工藝�����,而一些新技術����,如采用化學氣相沉積法制備鎢靶材,也時有報道���,但這些新技術還存在諸如成本高���、產(chǎn)品致密度低、 穩(wěn)定性差����、 濺射薄膜電阻率高等不足,阻礙了大規(guī)模的商業(yè)化應用���。

中國鎢礦資源儲量高居世界第一����, 但是制備集成電路用鎢濺射靶材的技術水平依然遠遠落后于世界先進水平, 相關產(chǎn)品嚴重依賴進口����。 隨著人工智能、大數(shù)據(jù)��、物聯(lián)網(wǎng)等高端科技的發(fā)展�,智能芯片和智能硬件的需求量劇增, 其中海量的數(shù)據(jù)需要大量的存儲設備�,所以高端鎢濺射靶材的研究���、制備和國產(chǎn)化變得越來越重要��。因此����,加強高純靶材制備的機

理研究�����,突破國外核心制備技術壁壘�����,對于高端靶材的國產(chǎn)化、 提升行業(yè)的發(fā)展自主性具有十分重要的意義���。

參考文獻:

[1]SUGURO K�����,NAKASAKI Y�����,INOUE T����,et al.Reaction kinetics in

tungsten/barrier

metal/silicon

systems

[J].Thin

Solid

Films���,

1988����,166:1-14.

[2] COLLINS J����,NARASIMHAN M K,LIU J�����,et al.High temperature

tungsten metallization process:US8617985 B2[P].2013-12-31.

[3] WSTS Semiconductor Market Forecast Fall 2019[EB/OL].San Jose,

California�,2019,https://www.wsts.org/.

[4] FAN V�����,HARMAN D�����,JEWETT J�,et al.Evaluation of process for

semiconductor

fabrication

materials

that

are

better

for

the

environment [J].Intel Technology Journal��,2008�����,12:69 -75.DOI:

10.1535/itj.1201.07.

[5]RADIC

N��,TONEJC

A����,IVKOV

J�����,et

al.Sputter -deposited

amorphous -like tungsten

[J].Surface & Coatings Technology�����,

2004��,180/181:66-70.

[6]GLEBOVSKY V G�����,MARKARYANTS E A�,TITOV E V.Deposition

of TiW thin films by magnetron co-sputtering[J].Materials Letters���,

1994����,21(1):89-93.

[7]GLEBOVSKY V G�����,YASCHAK V Y,BARANOV V V���,et al.

Properties of titanium-tungsten thin films obtained by magnetron

sputtering of composite cast targets [J].Thin Solid Films��,1995���,257

(1):1-6.

[8]YU Y,SONG J�����,BAI F��,et al.Ultra -high purity tungsten and its

applications [J].International Journal of Refractory Metals & Hard

Materials��,2015�����,53(part B):98-103.

[9]WINKLER J�,LINKE D C.Sputtering targets:The advantages of

powder metallurgy in the production process [J].Powder Metallurgy

Review�����,2018:73-87.https://www.pm-review.com/powder-metallurgy

-review -archive/2018 -archive/powder -metallurgy -review -

autumn-2018-vol-7-no-3/.

[10]SARKAR J.Sputtering materials for VLSI and thin film devices[M].

US:Elsevier Inc. Publisher,2013:315.

[11]MAILLE L����,SANT C,GARNIER P.A nanometer scale surface

morphology study of W thin films

[J].Materials Science and

Engineering:C����,2003,23(6/7/8):913-918.

[12]LO C F���,MCDONALD P�,DRAPER D����,et al.Influence of tungsten

sputtering target density on physical vapor deposition thin film

properties[J].Journal of Electronic Materials,2005�,34:1468-1473.

[13]LO C F,DRAPER D�����,GILMAN P S.Method of making high density

sputtering targets:US6165413[P].2000-12-26.

[14]DUNLOP J A�,YUAN J,KARDOKUS K���,et al.Sputtering target with

ultra-fine oriented grains and method of making same:US 5809393

A[P].1998-09-15.

[15]TAKAFUMI D�����,SHINICHIRO S.Tungsten target:WO 2018/179770

[P].2018-10-04.

[16]WATANABE K����,YABE Y,ISHIGAMI T��,et al.Tungsten sputtering

target and method of manufacturing the target:US7718117 [P].

2010-05-18.

[17]白峰.高純鎢合金靶材制備工藝的研究[D].廈門:廈門大學���,

2015.

BAI Feng.The study of preparing of high purity tungsten alloy

targets[D].Xiamen:Xiamen University��,2015.

[18]姚力軍����, 相原俊夫�����, 大巖一彥����, 等. 鎢靶材的制作方法:

103567444 A[P]. 2014-02-12.

[19]MATHAUDHU S N,DEROSSET A J�����,HARTWIGC K T�,et al.

Microstructures and recrystallization behavior of severely hot -

deformed tungsten[J].Materials Science and Engineering:A,2009��,

503(1/2):28-31.

[20]魏修宇��,黃江波��,龍堅戰(zhàn)�����,等.一種大尺寸高純鎢靶材及其生產(chǎn)

方法:201310670912.5[P].2013-12-12.

[21]雷繼鋒. 集成電路制造用濺射靶材綁定技術相關問題研究[J].

金屬功能材料�,2013,20(1):48-53.

LEI Jifeng.Research on bonding technology of sputtering target for

IC manufacturing [J].Metallic Functional Materials����,2013,20(1):

48-53.

[22]LO C F�,LEE F,GILMAN P S��,et al.Method of making high-density,

high-purity tungsten sputter targets:US 6328927 B1[P].2001-12-

11.

[23]SHIBUYA T�,TERAMOTO S,MATSUO S��,et al.Tungsten based

sintered compact and method for production thereof:US 2007/

0172378 A1[P]. 2007-07-26.

[24]SUZUKI S�����,MIYASHITA H.Tungsten target for sputtering and

method for preparing thereof:US 6582535 B1[P].2003-06-24.

[25]IVANOV

E

Y.High

purity

target

manufacturing

methods:

US8506882 B2[P].2013-08-13.

[26]NAKAHATA M.Tungsten target and method for producing same:

US 9388489 B2[P].2016-07-12.

[27]TAKUO I.Method of producing tungsten target for sputtering:JP

2003226964 A[P].2003-08-15.

[28]WATANABE K����,YABE Y,ISHIGMI T�,et al.Tungsten sputtering

target and method of manufacturing the target:US 2005/0029094

A1[P].2005-02-10.

[29]YI W,ROTHERS S T����,SUSAN D,et al.Methods of forming three-

dimensional PVD targets:WO 2006/055513 B1[P].2006-11-02.

[30]IVANOV E Y.High purity target manufacturing methods:WO

2006/001976 A3[P].2006-02-16.

[31]OHASHI K���,OKABE T.Tungsten sintered compact sputtering target

and tungsten film formed using same target:US 10047433 B2[P].

2018-08-14.

[32]KAMINAGA K�����,OHASHI K.Tungsten sintered compact sputtering

target and tungsten film formed using said target:US 2018/0261438

A1[P].2018-09-13.

[33]SUZUKI R����,ODA K.Tungsten sintered sputtering target:US2011/

0094879 A1[P].2011-04-28.

[34]SUZUKI R���,ODA K.Tungsten sintered sputtering target:US 2016/

014790 A1[P].2016-01-14.

[35]OHASHI K���,OKABE K.Tungsten sintered compact sputtering target

and method for producing same:US 9812301 B2[P].2017-11-07.

相關鏈接