引言

隨著集成電路不斷向大規(guī)模甚至超大規(guī)模發(fā)展,電子元器件尺寸越來(lái)越向微型化演變���,芯片特征尺寸也逐漸縮小到深亞微米和納米的水平[1]���。12英寸、微納米技術(shù)和銅工藝被稱為引導(dǎo)大規(guī)模集成電路發(fā)展趨勢(shì)的三大浪潮�����。傳統(tǒng)的6~8寸集成電路工藝都是主要采用了鋁作為金屬互聯(lián)材料�����,但是隨著器件特征尺寸的減小以及硅片載體規(guī)格的增加和集成度的提高���,鋁布線出現(xiàn)了電遷移嚴(yán)重、電阻率高等缺陷[2]����,這些缺陷嚴(yán)重時(shí)會(huì)導(dǎo)致電路板失效。后來(lái)人們又采用A1-Si�、A1-Cu、Al-Si-Cu等一系列以鋁為基體的鋁合金���,試圖解決上述問(wèn)題�����,但沒(méi)有成功��。銅及銅合金的出現(xiàn)給硅芯片的互連材料帶來(lái)了巨大的變化����,從根本上解決了上述問(wèn)題。它以低電阻率���、高導(dǎo)電性和布線工藝步驟少等優(yōu)勢(shì)在大規(guī)模邏輯芯片的高端應(yīng)用上優(yōu)勢(shì)明顯[2-6]���。銅工藝與鋁工藝完全不同。銅工藝是采用嵌入式工藝得到圖形化的導(dǎo)線����。上下層銅導(dǎo)線之間通過(guò)微通孔(via)互相連接,微通孔是通過(guò)另外一層光刻和蝕刻步驟形成的�。目前國(guó)際主流技術(shù)已從65nm技術(shù)向45~28nm轉(zhuǎn)移。高純銅及其合金作為濺射靶材在大規(guī)模集成電路制造中主要用于包括接觸���、通孔�、互連線、阻擋層等PVD鍍膜[7]����。

1、大規(guī)模集成電路用高純銅靶在互聯(lián)工藝中的作用

國(guó)際上銅布線工藝都采用的是“大馬士革”(Damascene)結(jié)構(gòu)的鑲嵌工藝����。該技術(shù)是先在介質(zhì)層材料中刻槽,然后沉淀阻擋層以及銅籽層�,接著沉淀銅,最后使用CMP技術(shù)把多余的銅以及阻擋層材料去除���。銅布線過(guò)程包括阻擋層與種子層的沉積和銅的電化學(xué)鍍[1]����。目前�����,阻擋層及種子層的沉積主要是利用PVD工藝進(jìn)行��,相應(yīng)的濺射銅靶材的要求為:晶粒尺寸小于50μm����,純度99.9999wt%(6N)以上,晶粒取向有嚴(yán)格的要求��。銅互聯(lián)工藝大幅度提高了芯片的集成度�����,器件密度和時(shí)鐘頻率以及降低了能量的消耗�����,特別是在邏輯控制芯片的高端應(yīng)用(90nm及以下)方面優(yōu)勢(shì)非常明顯�����。

2�����、大規(guī)模集成電路用高純銅靶材的分類

從目前的相關(guān)資料可知[8-1]�,大規(guī)模集成電路用高純銅靶材主要分為:高純銅靶材和高純銅合金靶材兩大類,其中銅的純度都要滿足大于99.9999wt%(6N)��。90~45nm之間主要以高純銅靶材為主��,但是對(duì)于布線寬度為45nm及以下,縱橫尺寸比超過(guò)8的超精細(xì)布線����,種子層(Seed)厚度變?yōu)?0nm以下的極薄膜,用6N超高純銅靶形成種子層的場(chǎng)合���,就會(huì)產(chǎn)生凝聚���,不能形成良好的種子層,而且電遷移問(wèn)題也愈顯嚴(yán)重�。因此,研究者引入銅合金靶材來(lái)抑制電遷移��,提高銅種子層的穩(wěn)定性和均勻性���,同時(shí)避免電鍍期間出現(xiàn)凝聚物的現(xiàn)象[8]���。

在高純銅中加入一種或多種合金元素能夠更好地控制高純銅靶材的晶粒尺寸,同時(shí)也能夠保證銅靶材晶粒尺寸的均勻性�,提高靶材本身的強(qiáng)度和穩(wěn)定性。但是����,由于合金元素的存在影響銅的電阻率,所以通常將靶材內(nèi)合金化元素的總量限制為小于10wt%�����。對(duì)于有特定用處的銅薄膜和內(nèi)部連線�����,需要與高純銅相匹配的電阻率����,將合金化的量限制為不大于3wt%。目前主要的銅合金靶材為Cu-Al�、Cu-Sn、Cu-Mn和Cu三元及多元合金靶材���。與純銅相比���,采用合金化的方式可以降低電遷移、應(yīng)力遷移���、腐蝕和氧化性等一些副作用�����,同時(shí)在含銅導(dǎo)電材料中仍保持低的總電阻�。

3、大規(guī)模集成電路用高純銅合金靶材

3.1高純cu-Al和cu-sn合金靶材

銅的電遷移特性雖然比鋁有所改善���,但是仍然不能令人滿意���。在銅中摻入少量合金元素,如鋁����、錫等,可進(jìn)一步改善其電遷移特性��。鋁元素在集成電路工藝中早已廣泛使用�,該技術(shù)簡(jiǎn)單,便于引入銅互連工藝中���。錫能夠得到最佳的電遷移特性�,因此���,銅鋁合金和銅錫合金的淀積是目前基于銅金屬互連領(lǐng)域的一個(gè)研究重點(diǎn)�。但是引入合金元素通常會(huì)導(dǎo)致金屬電阻率的提高��。例如,銅中摻入錫����,其電阻率提高系數(shù)高達(dá)2.88μΩ.cm-1/%�,線性范圍是2.69%。因此�,合金元素的濃度要適中,一般應(yīng)低于1%[15]���。

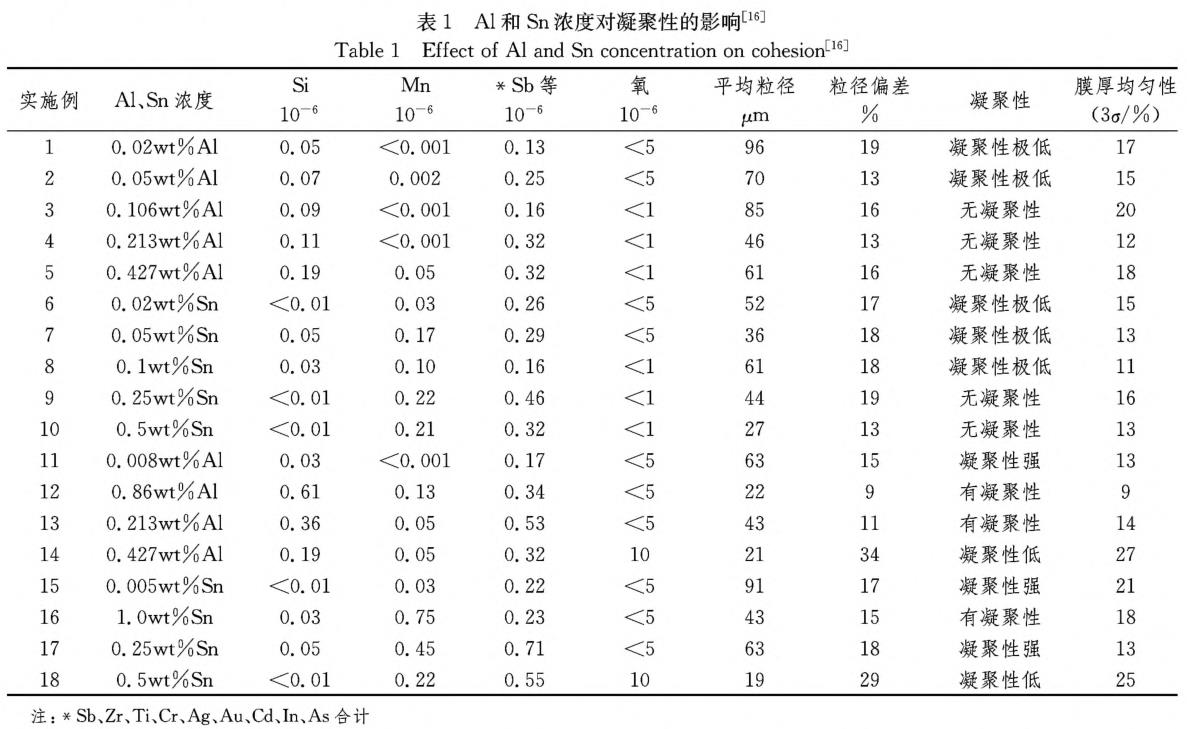

銅種層變?yōu)楹穸?0nm以下的極薄膜時(shí)����,6N純銅靶材在濺射成種子層時(shí)極易產(chǎn)生凝聚�����,不能形成良好的種子層�����,因此多個(gè)專利[16-18]在高純銅中加入0.5wt%~4wt%的Al或Sn來(lái)防止這種情況���。銅種層的均勻形成很重要����,在基礎(chǔ)層凝聚的場(chǎng)合,由電鍍形成銅膜時(shí)���,就不能形成均勻的膜��。例如���,在布線中會(huì)形成空隙、斷線等情況�����。即使沒(méi)有殘留上述空隙等缺陷���,由于該部分形成了不均勻的銅電沉積組織����,因而也會(huì)產(chǎn)生電遷移抗性降低的問(wèn)題���。為了解決該問(wèn)題��,在銅電鍍時(shí)形成穩(wěn)定均勻的種層很重要�,而為形成濺射成膜特性好的種層,銅中加入0.5wt%~4wt%的Al或Sn元素非常有效(表1)��。

在制備高純Cu-Al和Cu-Sn合金靶材過(guò)程中關(guān)鍵是制備低含量的Cu-Al和Cu-Sn合金鑄錠���,由于Al和Sn的含量比較低,極易在鑄造過(guò)程中產(chǎn)生合金元素的分布不均勻和成分偏析�,導(dǎo)致濺射過(guò)程出現(xiàn)質(zhì)量問(wèn)題。通常在鑄造過(guò)程中通過(guò)高速攪拌和電磁攪拌等多種方法保證微量元素的均勻性����,也可以通過(guò)后續(xù)的合適熱處理溫度和時(shí)間保證元素的均勻性。Al和Sn元素的加入有兩種方式:一種是單質(zhì)高純Al或Sn的直接加入��;另一種是先制備出高純Cu-Al和Cu-Sn中間合金����,然后加入熔煉爐。由于Al���、Sn和高純銅的熔點(diǎn)相差較大��,為了保證成分的均勻性�����,通常采用中間合金的加入方式���。

3.2高純Cu-Mn合金靶材

高純Cu-Mn合金靶材也是即將被廣泛采用的12寸集成電路靶材���,Koike等[18]指出Cu-Mn合金主要用來(lái)制作銅種子層;在高純銅中添加少量的Mn元素��,由于Cu和Mn原子的擴(kuò)散速度不同�����,Mn會(huì)在Cu和Si基片之間形成自擴(kuò)散層�,防止濺射材料與硅基片的反應(yīng),同時(shí)優(yōu)化生產(chǎn)過(guò)程[19]�。

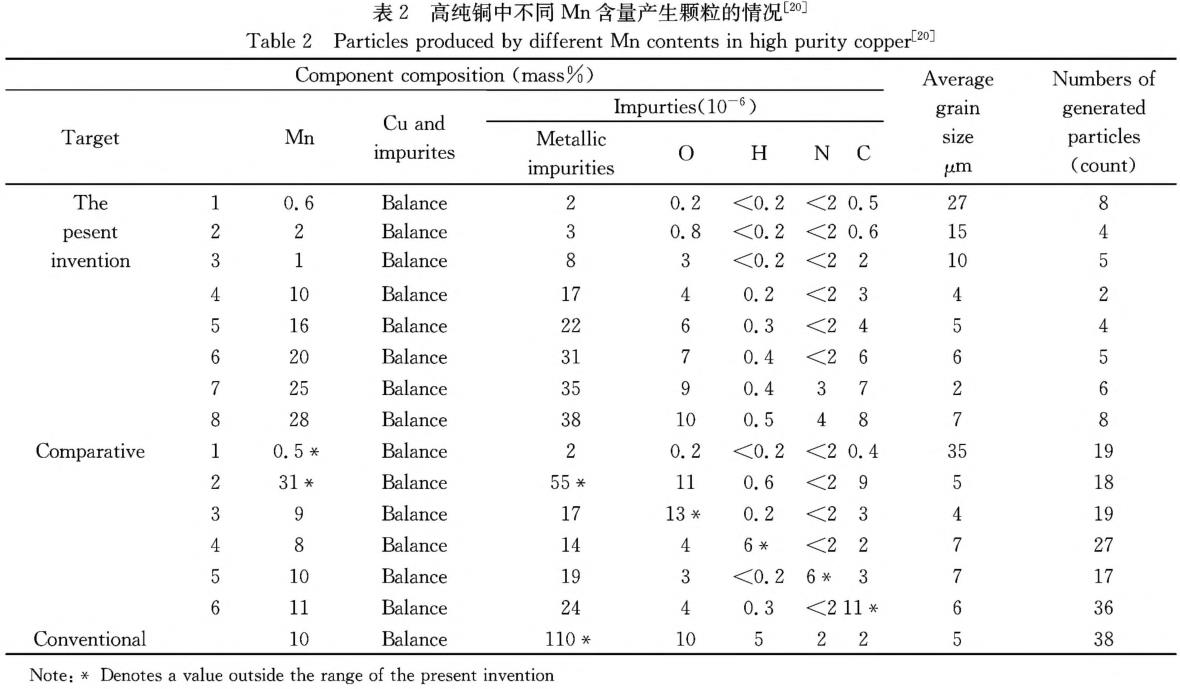

ShojiAoki等[18]比較了不同Mn含量(0.6wt%~30wt%)的高純銅靶材產(chǎn)生顆粒的情況。Cu-Mn合金主要適用于濺射種子層(表2)�。

2014年霍尼韋爾采用等徑角塑性(ECAE)技術(shù)制備了新型銅錳濺射靶材。ECAE技術(shù)最初是為Al及Al合金靶材研發(fā)的生產(chǎn)工藝�。通過(guò)該工藝使得銅靶材具有超細(xì)的晶粒尺寸,材料更加均勻��,硬度更高��,雜質(zhì)更少�����。新型ECAE銅錳合金靶材晶粒尺寸是亞微米,遠(yuǎn)小于普通靶材的尺寸50肚m���。超細(xì)晶粒尺寸能夠有效避免半導(dǎo)體生產(chǎn)商在采用普通帶背板設(shè)計(jì)靶材時(shí)碰到的濺射電壓突然降低問(wèn)題�����。靶材硬度增加可以采用單體設(shè)計(jì),不需要背板支撐��,這樣靶材的使用壽命延長(zhǎng)了一倍�����,提高了靶材利用率以及濺射工藝的生產(chǎn)效率����,降低了企業(yè)成本。

3.3三元或多元Cu合金靶材

通過(guò)熔鑄的方法在高純銅中加入Ag�����、Al���、Ca�、Fe、Ga�、Mn、Ni�����、Pt��、Sb��、Sc��、Sn�����、Ta���、Ti��、W���、Zn和Zr等元素中的至少兩種��,可以制備三元或多元銅合金靶材[20-23]����。

與二元合金相比�����,采用三元或者多元合金能夠解決很多具體問(wèn)題且具有靈活性�。利用多元合金元素的不同物理化學(xué)特性,在濺射鍍膜過(guò)程中起到特殊的效果��。例如��,當(dāng)向高純銅中添加特定元素時(shí)�,可降低電遷移�,而其他元素可以降低腐蝕性。因此���,當(dāng)形成二元合金時(shí)���,該合金一般適合用來(lái)降低電遷移或降低腐蝕,但很少二者兼顧。然而��,采用三元或多元合金可使電遷移和腐蝕都得到解決�����,因而能夠根據(jù)不同的技術(shù)要求和特點(diǎn)來(lái)設(shè)計(jì)合金靶材的產(chǎn)品種類����,這些組合能夠解決很多方面的問(wèn)題。

采用三元或多元合金的另一個(gè)好處是��,通過(guò)合金化使得靶材的強(qiáng)度得到極大提高����,使得靶材的壽命更長(zhǎng)。高強(qiáng)度的靶材能夠承受更大的濺射功率��,優(yōu)化背板材料��,提高靶材的使用壽命和濺射效果��。

4��、展望

大規(guī)模集成電路的制程工藝趨向于朝密集度愈高的方向發(fā)展����。密度愈高的IC電路設(shè)計(jì)�����,意味著在同樣大小面積的IC中�����,可以擁有密度更高�����、功能更復(fù)雜的電路設(shè)計(jì)�����。微電子技術(shù)的發(fā)展與進(jìn)步�����,主要是靠工藝技術(shù)的不斷改進(jìn),使得器件的特征尺寸不斷縮小��,從而不斷提高集成度����,降低功耗����,提高器件性能����。芯片制造工藝在180~130nm之問(wèn)主要采用的是高純鋁和鋁合金靶材;在90~65m之間主要采用的是高純銅靶材����;在45~28nm甚至是22nm主要采用的是高純銅鋁和銅錳合金靶材;然而進(jìn)入20nm以下的高端工藝后��,無(wú)論是鋁�����、銅及其合金的表現(xiàn)其實(shí)都很不理想�。而金屬元素鈷在填滿能力、抗阻力�����、可靠度三方面的優(yōu)勢(shì)明顯�����,特別是在布線寬度7nm以下時(shí),鈷金屬成為了新的王者���。但是��,目前銅及銅合金靶材仍然在300mm大規(guī)模集成電路中大量使用��,特別是高端通用領(lǐng)域?qū)Ω呒冦~合金靶材的材料純度(大于99.99995wt%)�、組織均勻性���、合金元素分布的均勻性�����、晶粒尺寸以及焊接強(qiáng)度的要求也越來(lái)越高�����。目前國(guó)際上能夠批量供應(yīng)這類銅合金靶材的廠家還只有日本和美國(guó)的兩家公司����。這也是我國(guó)高端高純銅合金領(lǐng)域生產(chǎn)企業(yè)開發(fā)高附加值新產(chǎn)品的一個(gè)重要方向����。

相關(guān)鏈接